# Design and Implementation of FIR Filter to analyze Power Efficiency and Delay Reduction

<sup>1</sup>Shilpa.V, <sup>2</sup>Srithal.B.S, <sup>3</sup>Preethi.G.Deshpande, <sup>4</sup>Meghana.A <sup>1,2,3,4</sup>Dr Ambedkar Institute Of Technology, Bengaluru

Abstract: With the design of finite impulse response FIR filter utilising adder, coefficients and multiplication are considered. Herein, an algorithm like multiple constant multiplications is considered in FIR type, predominently to minify the complexity arised in the circuit, delay which is being increased and the multiplication accumulated large portion of area. These problems can be considered with modern technique, which are named as digit serial multiple type and constant multiplication. Hence, this reduces unnecessary complexity, delay and utilization of an area. Along with this, we can know modified carry select adder is being implimented in the current paper. In this work, it is examined thatthere is ten to twenty gradual appreciation in the efficiency of power and surprising reduction in the delay, which are compared to techniques as existed.

#### I. INTRODUCTION

The process of multiplication in the respective digital system is literallyamalgamation of addition and operation of shifting, which utilises more at inclusion of machine cycles and executes less multiplication for the reason of iteration. For problems of iteration, these MCM is widely considered in utilisation of adders of different type. This results literally, no solution in perfection for bringing the efficiency of power and the delay therein. Hilbert transfiguration leads to issues, which include latency, results being delayed, much time required and even consumption of power being kept at high. Bull and horrocks method was successful which is performed by Dempster et al. Gallagher et al considered producing high multiplier which provided better results in reference to delay but complexity problem was not solved with area selection. Canonical signed digit was herein considered, where program is

saving upto half the cent percent and expression in common is upto thirty three percent, which is program count is saved.

#### II. PROPOSED WORK

From the study, products of partial type in GB type algorithm follows to an appropriate results of area, which is being minimised at the gate level. With the bit type parallel algorithm, there is possibility of hardware being not required. Digit type serial operators prefer lesser area. Dflip flops are considered in shifting type operation. Sign digit is considered which actually helps in minifying the accumulation of area, speedy type structure in arithmetic form and hence reduction in consumption of area. Boolean function is integral part of the system, when considering the implementating or executing at the circuit. Digital series type arithmetic can be chosen along. Two Ripple Carry Adder gives an output along with the full adder circuit. Full Adder is utilised for binary numbers addition and gives out two output sum and therein at carry. Error in amalgamation is reduced. The operation of subtraction is executed initialising of the type D flip flop.

#### III. METHODOLOGY

Different methodology is worked out. Full adder and subtractor are considered. Herein, variable numbers are reduced and multiplication speed improves. Subtraction operation is worked with the method full subtractor 2. Also, full adder and subtractor type or method is worked out. Sifting and the corresponding adding operation are considered herein. BEC method is implemented in VHDL coding and executed using the Xilinx software.

ISSN (Print): 2278-8948, Volume-5 Issue-6 2016

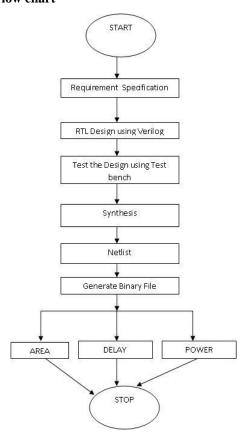

3.1 Flow chart

IV. IMPLEMENTATION

For FIR type filter, realization as per the frequency in response to hardware and software must be kept in right format considering time factor. In coming to software implementation, direct and optimised format alone is utilised. Processing by digital type signal plays a vital role, at the same plane phase, which comes in across with the feed type forward, at an implementation level.

#### V. HARDWARE REQUIREMENTS

High performance processor is considered herein with complete system set up. Along with the components respective type FPGAs or VLSI of FIR filters are needed.

## VI. SOFTWARE REQUIREMENTS

Xilinx software is chosen here. This software is primary utilised for synthesis of circuit and design. Slide picture is showcased below.

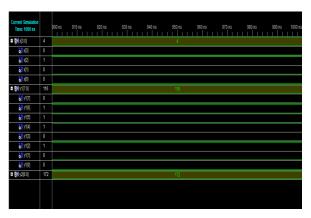

Fig: Simulation output

The above screen shot shows the difference between the two techniques (CSE and GB). It shows the number of the cycle's in utilization and the amount of data utilized by the particular variables.

#### VII. ADVANTAGES

Officially, this software supports windows OS. Designs can be synthesized, examination with respective to time and target device can be made and an associated or being linked to the programmer. Project time and cost can be immensely reduced.

#### VIII. DISADVANTAGES

This software cannot be considered for the FPGA products.

#### IX. RESULTS

In this work, primary focus is on reduction of the power in consumption and delay along reduction in an area. In this, the BEC method is utilised to simplify an addition as well as the GB method considered, which produces great output utilising less number of resources for computation.

#### X. CONCLUSION

FIR filter is literally a significant part of the considered system of DSP and it is widely considered and executed to any VLSI and circuits of communication. In the present research, method of GB along gives satisfactory results. Efficiency of power has increased to fifty six percentages and sixty four percentages in CSE and GB with respect when made in comparison to CSE and GB utilising CSA. Work is constrained to simulation alone. There would be certainly more impact in this research.

## XI. FUTURE SCOPE

Scope in future lies with the techniques considered. We have concluded that some methods gives clues for prospects and some others not. Every technique has errors included, which are in relation to time, delay and power. We can infer that the scope is limited.

### **REFERENCES**

- [1] J. McClellan, T. Parks, and L. Rabiner, "A computer program for designing optimum FIR linear phase digital filters," Audio Electroacoust. 1973.

- [2] A. G. Dempster, S. Member, M. D. Macled, and A.G. Representation, "Blocks in FIR Digital Filters," vol. 42, no. 9, 1995.

- [3] W. L. Gallagher and E. E. Swartzlander, "High Radix Booth Multipliers Using Reduced Area Adder Trees," pp. 545–549, 1995.

- [4] R. I. Hartley, "Subexpression Sharing in Filters Using Canonic Signed Digit Multipliers," vol. 43, no. October, 1996.

- [5] H. T. Nguyen and A. Chatterjee, "Number-Splitting with Shift-and-Add Decomposition for Power and Hardware Optimization in Linear DSP Synthesis," vol. 8, no. 4, pp. 419–424, 2000.

- [6] M. Potkonjak, M. B. Srivastava, and A. P. Chandrakasan, "Multiple Constant Multiplications: Efficient and Versatile Framework and Algorithms for Exploring Common Subexpression Elimination," IEEE Trans. Comput. Des.Integr.CIRCUITS Syst., vol. 15, no. 2, 1996.

- [7] H. Applications, J. Park, W. Jeong, H. Mahmoodi-meimand, S. Member, Y. Wang, H. Choo, and K. Roy, "Computation Sharing Programmable FIR Filter," vol. 39, no. 2, pp. 348–357, 2004.

- [8] Y. Voronenko and M. Püschel, "Multiplierless multiple constantmultiplication," ACM Trans. Algorithms, vol. V, pp. 1–39, 2005.

- [9] L. Aksoy, S. Member, E. Costa, and P. Flores, "Exact and Approximate Algorithms for the Optimization of Area and Delay in Multiple Constant Multiplications," vol. 27, no. 6, pp. 1013–1026, 2008.

- [10] Z. Milivojević, "FIR Filter," in Digital Filter Design, 1st ed., MikroElektronika, 2009.

- [11] L. Aksoy, C. Lazzari, E. Costa, P. Flores, and J. Monteiro, "Efficient shift-adds design of digit-serial multiple constant multiplications," Proc. 21st Ed. Gt. lakes Symp. Gt. lakes Symp. VLSI GLSVLSI '11, vol. 2, p. 61, 2011.

- [12] I. Koren, Computer Arithmatic Algorithms. A.K.Peters ltd., 2002.

- [13] T. Larrabee, "Test Pattern Generation Using Boolean Satisfiability," vol. 11, no. 1, pp. 4–15, 1992.

- [14] L. Aksoy, C. Lazzari, E. Costa, P. Flores, J. Monteiro, and S. Member, "Design of Digit-Serial FIR Filters: Algorithms, Architectures, and a CAD Tool," vol. 21, no. 3, pp. 498–511, 2013.

- [15] "Digital Filter Design." [Online]. Available: http://www.mikroe.com/chapters/view/72/chapt er-2-fir-filters/#id24.

- [16] L. Tag and Jiang jean, Digital Signal processing. 2013, p. 896.

- [17] J. Gurung, Signals and System. 2009, p. 636.

- [18] L. Aksoy, C. Lazzari, E. Costa, P. Flores, and J. Monteiro, "Optimization of area in digit-serial Multiple Constant Multiplications at gate-level," 2011 IEEE Int. Symp. Circuits Syst., vol. 2, pp. 2737–2740, May 2011.